#### **DESCRIPTION**

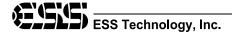

The ES1868 Audiprive is a single, mixed-signal digital audio chip that can be designed into a motherboard, add-in card, or integrated into other peripheral cards to provide stereo sound and FM music synthesis to personal computers. The ES1868 can record, compress, and play back voice, sound, and music using built-in mixer controls. It also supports Plug and Play (PnP) standard and provides Plug and Play configuration for the following logical devices: CD-ROM (IDE), Modem, and a general-purpose I/O device.

The ES1868 contains an embedded microprocessor, 20-voice ESFM music synthesizer, 16-bit stereo wave ADC and DAC, 16-bit stereo music DAC, MPU-401 serial port, dual game ports, two serial interfaces to external DSP and external wavetable music synthesizer, DMA control logic with FIFO, ISA bus interface logic, and hardware master volume control. An internal preamp accepts 3 stereo inputs and a mono microphone input.

The Advanced Power Management (APM) features include suspend/resume from disk or host-independent, self-timed power-down and automatic wake-up.

A DSP serial interface allows an external DSP to take over resources such as ADC or DACs. Control of I/O address, DMA, and interrupt selection can be by jumper or through c

- Program the playback DMA channel for monophonic, 16-bit playback, auto-initialize mode. Set the 2's complement transfer count for 64 bytes. Since the second channel is in auto-initialize mode, but the second channel interrupt is not being used, any value for the transfer count can be used. Using 64 bytes for the value allows the playback channel to get a "head start" on the record channel by polling the second channel interrupt request bit after starting the second channel DMA.

- Before starting the second channel DMA, clear the second channel interrupt request bit by writing a 0 to bit 7 of Mixer Extension register 7Ah.

- Enable full-duplex mode by setting bit 0 of Mixer Extension register 78h. Since the playback FIFO is presumably empty, the value 0 is transferred to the playback DAC at each sample clock. It is possible that a click or pop will be heard when full-duplex mode is enabled. To prevent this, use the D1h command to enable the DAC input to the mixer after a suitable delay (for example, 25 milliseconds).

- Enable playback DMA by setting bit 1 of Mixer Extension register 78h. After 64 bytes are transferred, bit 7 of 7Ah will go high. Poll this bit with a suitable time-out (for example, 10 milliseconds).

- After bit 7 of 7Ah goes high, enable recording by setting bit 7 of Extended Mode register B7h and bit 0 of Extended Mode register B8h.

- The first 50-100 milliseconds of recorded data should be discarded until analog circuits have settled.

- 2. To exit full-duplex mode, clear bits 0 and 1 of Mixer Extension register 78h.

The following discusses the registers relevant to full-duplex operation.

## **DMA-Related Mixer Extension Registers**

The following registers control DMA operations:.

Table 4 DMA-Related Programming Registers

| Address | Name                                                  |

|---------|-------------------------------------------------------|

| 74h     | Second DMA Transfer Count Reload register – low byte  |

| 76h     | Second DMA Transfer Count Reload register – high byte |

| 78h     | Second DMA control 1                                  |

| 7Ah     | Second DMA control 2                                  |

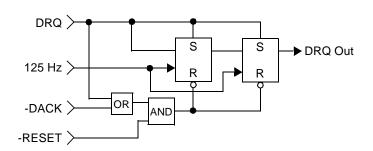

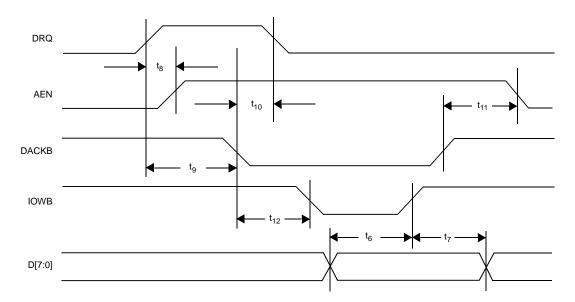

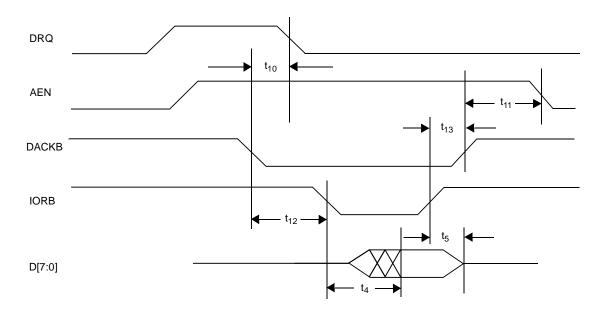

#### **DRQ Latch Feature**

This feature is enabled when bit 7 of PnP Vendor-Defined Card-Level register 25h is high.

If this feature is enabled, each of the three audio DRQs will be latched high until one of the following occurs:

- A DACK low pulse occurs while DRQ is low or goes low due to a DACK pulse.

- · A hardware reset occurs.

- 8-16 milliseconds elapse while DRQ is low.

Figure 6 DRQ Latch

#### **INTERRUPTS**

There are seven interrupt sources in the ES1868:

Audio 1 Used for the first DMA channel (Sound Blaster-compatible DMA, Extended Mode DMA, and Extended Mode programmed I/O), as well as Sound Blaster-compatible MIDI receive. Extended register B1h controls use of this interrupt for extended mode DMA and programmed I/O. This interrupt request is cleared by hardware or software reset, or an I/O read from port Audio\_Base+0Eh. The interrupt request can be polled by reading from port Audio\_Base+0Ch. This interrupt is assigned to an interrupt channel by PnP register 70h of LDN 1

Audio 2 Optional for the second DMA channel. The ES1868 can operate in full-duplex mode using two DMA channels. However, the second DMA channel must share the same sample rate as the first DMA channel. For this reason it is not necessary to use a separate interrupt for the second DMA channel, but it can be done. This interrupt is masked by bit 6 of Mixer Extension register 7Ah. It can be polled and cleared by reading or writing bit 7 of the same register. This interrupt is assigned to an interrupt channel by PnP register 72h of LDN 1.

#### Hardware Volume

Hardware volume activity interrupt. This interrupt occurs when one of the three hardware volume controls generates an event. Bit 1 of Mixer Extension register 64h is the mask bit for this interrupt. The interrupt request can be polled by reading bit 3 of the same register. The interrupt request is cleared by writing any value to register 66h. This interrupt is assigned to an interrupt channel by PnP register 27h. Typically this interrupt, if used, is shared with an audio interrupt.

#### MPU-401

This interrupt occurs when a MIDI byte is received. It will go low when a byte is read from the MIDI FIFO and go high again quickly if there are additional bytes in the FIFO. The interrupt status is the same as the read data available status flag in the MPU-401 status register. This interrupt is masked by bit 6 of Mixer Extension register 64h. This interrupt is assigned to an interrupt channel in one of two ways: If the MPU-401 is part of the audio device, then PnP register 28h is used to assign the MPU-401 interrupt. If the MPU-401 is its own logical

device, it can also be assigned to an interrupt via PnP register 70h of LDN 3. Both these methods access the same physical register.

CD-ROM This source is the input pin CDIRQ.

Modem This source is the input pin MMIRQ.

#### General-Purpose

This source is the input pin GPI. If GPI is used for a DMA request for one of the devices CD-ROM, Modem, or General-purpose, then this pin can not be used as a general-purpose device interrupt.

Interrupt sources are mapped to one of the five interrupt output pins through the PnP registers. A given pin can have zero, one, or more interrupts mapped to it. Each PnP pin is assigned to an ISA interrupt channel number by Vendor-Defined Card-Level PnP registers 20h, 21h, and 22h. These registers are automatically loaded from the 8-byte header in the PnP configuration data.

Each interrupt pin can be in either an active or highimpedance state.

If a given interrupt pin has one or more sources assigned to it, and one or more of those sources is activated (register 30h, bit 0), then the interrupt pin will be active, that is, it will always be driving high or low. (An exception is the Modem interrupt, which can be deactivated if input MMIEB is high or if the Modem device is not active.) Each interrupt also has one or more mask bits that are AND'ed with the interrupt request.

## **Interrupt Status Register**

Register 6h of the configuration device can be read to quickly find out which ES1868 interrupt sources are active. The bits are:

Table 5 Interrupt Status Bits in Configuration Register 6

| Bit | Description                                                                         |  |  |  |

|-----|-------------------------------------------------------------------------------------|--|--|--|

| 0   | Audio 1 interrupt request                                                           |  |  |  |

| 1   | Audio 2 interrupt request AND'ed with bit 6 of Mixer Extension register 7Ah         |  |  |  |

| 2   | Hardware volume interrupt request AND'ed with bit 1 of Mixer Extension register 64h |  |  |  |

| 3   | MPU-401 receive interrupt request AND'ed with bit 6 of Mixer register 64h           |  |  |  |

| 4   | CDIRQ input pin                                                                     |  |  |  |

| 5   | MMIRQ input pin AND'ed with inverse of MMIEB input                                  |  |  |  |

| 6   | GPI input pin                                                                       |  |  |  |

## Interrupt Mask Register

Register 7h of the configuration device can be used to mask any of the seven interrupt sources.

The mask bits can be used to force the interrupt source to be zero, but they do not put the interrupt pin in a high-impedance state. Each bit is AND'ed with the corresponding interrupt source. This register is set to all ones by hardware reset.

The Interrupt Status Register (ISR) is not affected by the state of the Interrupt Mask Register (IMR). That is, the ISR reflects the status of the interrupt request lines before being masked by the IMR.

The IMR is useful when interrupts are shared. For example, assume that Audio 1, Audio 2, Hardware Volume, and MPU-401 all share the same interrupt in Windows. When returning from Windows to DOS, the Hardware Volume, MPU-401, and Audio 2 interrupts can be masked by setting the appropriate bits to 0.

A second use is within an interrupt handler. The first thing the interrupt handler can do is mask all the interrupt sources mapped to the interrupt handler. Then, the ISR can be polled to decide which sources to process. Just before exiting the interrupt handler, the IMR can be restored. If an unprocessed interrupt remains active, it will generate an interrupt request because the interrupt pin was low during the masked period and then went high when the interrupt sources were unmasked. Also, while the interrupts are masked, the individual interrupt sources can change state any number of times without generating a false interrupt request.

## **Sharing Interrupts**

Plug and Play does not support sharing of interrupts in its resource assignment decision making. If a device wants to share an interrupt with another device that has been assigned an interrupt via PnP, the first device cannot request an interrupt for itself.

A logical device that supports interrupts can be assigned to an interrupt after the PnP sequence by the Windows driver. Refer to the "Bypass Key" section for information on the PnP sequence. In this case, it would typically be forced to share an interrupt with the first audio interrupt. For most cases, this is done simply by programming the appropriate PnP register (70h or 72h) for the selected device. However, there are two special cases.

- The hardware volume interrupt. This interrupt source can be assigned to an interrupt through Vendor-Defined Card-Level register 27h.

- The MPU-401 interrupt. This device is either part of the audio device or its own logical device. If it is part of the audio device, the interrupt can be assigned by writing to Vendor-Defined Card-Level register 28h. If this device is its own logical device, it is assigned an interrupt by either register 28h or register 70h of LDN 3.

#### PERIPHERAL INTERFACING

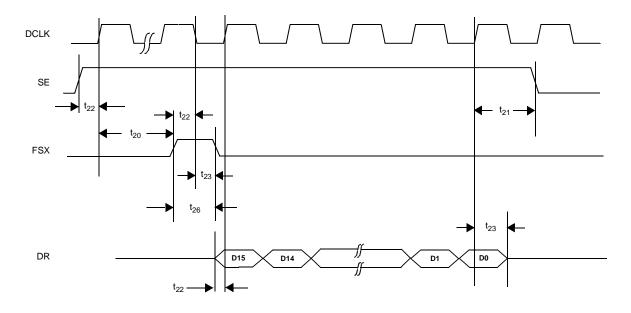

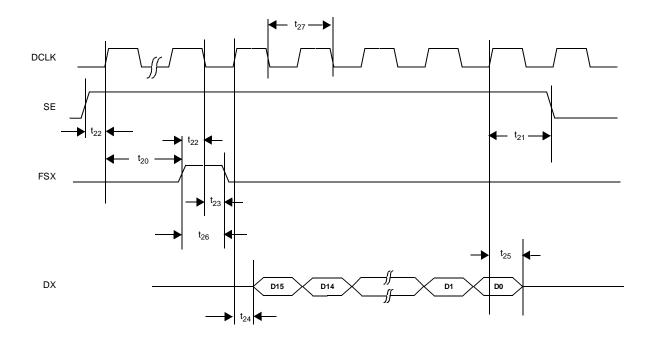

#### **DSP/Wavetable Interface**

The ES1868 contains a synchronous serial interface for connection to an external DSP or a wavetable music synthesizer.

#### **Applicable Pins**

Table 6 identifies pins in the DSP/Wavetable interface.

Table 6 DSP and Wavetable Interface Pins

| The following pins are used for interface with an external DSP chip: |                                                                                                 |                                                                                                                                                                                                                                                                |  |  |  |  |

|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| SE                                                                   | SE Input with Active-high signal from an external pull-down DSP to enable serial mode.          |                                                                                                                                                                                                                                                                |  |  |  |  |

| DCLK                                                                 | Input with pull-down                                                                            | Data clock. The rate can vary, but a typical value is 2.048 MHz (8 kHz x 256).                                                                                                                                                                                 |  |  |  |  |

| DX                                                                   | Tri-state output                                                                                | Data transmit. Active output when data is being transmitted serially from the ES1868, otherwise high-impedance.                                                                                                                                                |  |  |  |  |

| DR                                                                   | Input with pull-down                                                                            | Serial data input.                                                                                                                                                                                                                                             |  |  |  |  |

| FSX                                                                  | Input with pull-down                                                                            | Frame sync transmit. FSX is either active-high or active-low based on bit 3 of Mixer Extension register 48h. The FSX pulse is a request from the external DSP to begin transmission of 8 or 16 bits of data out of pin DX.                                     |  |  |  |  |

| pull-down active-high or ac<br>3 of Mixer Exten<br>FSR pulse signa   |                                                                                                 | Frame sync receive. FSR is either active-high or active-low, based on bit 3 of Mixer Extension register 48h. The FSR pulse signals the arrival of 8 or 16 bits of data to pin DR.                                                                              |  |  |  |  |

| The follo                                                            | wing pins are                                                                                   | used for interface with the ES689/ES690:                                                                                                                                                                                                                       |  |  |  |  |

| MCLK                                                                 | MCLK Input with pull-down Serial clock from external ES689/ ES690 music synthesizer (2.75 MHz). |                                                                                                                                                                                                                                                                |  |  |  |  |

| MSD                                                                  | Input with pull-down                                                                            | Serial data from external ES689/<br>ES690 music synthesizer. When both<br>MCLK and MSD are active, the stereo<br>DACs that are normally used by the<br>FM synthesizer are acquired for use by<br>the external ES689/ES690. The<br>normal FM output is blocked. |  |  |  |  |

## **Applicable Registers**

This section lists the Mixer Extension registers related to the DSP and wavetable serial interface operation. These registers are accessed via I/O addresses 2x4h and 2x5h.

Table 7 DSP and Serial Interface Programming Registers

| Address | Name                                     |  |  |

|---------|------------------------------------------|--|--|

| 42h     | Serial mode input control                |  |  |

| 44h     | Serial mode output control               |  |  |

| 46h     | Serial mode miscellaneous analog control |  |  |

| 48h     | Serial mode miscellaneous control        |  |  |

| 4Ch     | Serial mode filter divider               |  |  |

| 4Eh     | Serial mode format/source/target         |  |  |

## **DSP Operating Modes**

The DSP interface can be operated in either of two data transfer modes.

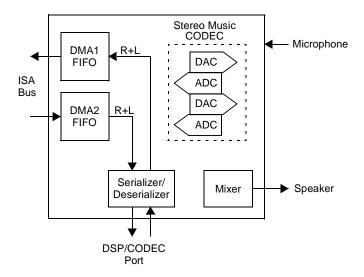

#### Full-Duplex DMA Mode

In this mode, the ES1868's DMA channels are operated in full-duplex (see Figure 7). The DSP port is enabled for mono, 16-bit, receive target = FIFO, and transmit source = FIFO. The sample rate is determined by the externally generated frame sync receive pulses (FSR). In this mode, FSX must equal FSR.

Data transferred via the second DMA channel is written into the second DMA FIFO. From there it is read out one word at a time based on a signal generated from the FSR pulse. The data is transmitted out the DX pin to an external 16-bit CODEC or DSP.

Data received on the DR pin from an external 16-bit CODEC is transferred into the first DMA channel FIFO at a time based on a signal generated from the FSR pulse. From there the data is read out of the first DMA FIFO via first channel DMA cycles.

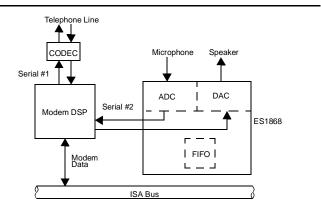

A typical application of this feature is a software, host-based Modem.

Figure 7 Full-Duplex Mode

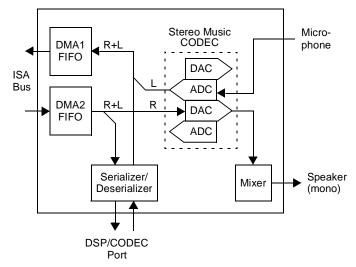

#### Interleave Mode

A typical application of the Interleave Mode is a software, host-based speakerphone, as shown in Figure 8. The host receives data from the phone line, and transmits it to the speaker. It also receives data from the microphone, performs acoustic echo cancellation, and transmits the result to the phone line.

Stereo data is received by the host via the first DMA channel. The "left channel" data comes from the microphone, the "right channel" data comes from the external CODEC.

Stereo data is sent to the ES1868 via the second DMA channel. The "left channel" data is transmitted to the CODEC, the "right channel" data is sent to the speaker.

The Interleave Mode is enabled when both full-duplex DMA is enabled, including the DSP serial interface, and bit 0 of Mixer Extension register 48h is set high.

While the sample rate is determined by the external CODEC, for best results it is recommended to set bit 7 of extended register A1h high. This minimizes jitter between the asynchronous external sync pulses and internal clocks.

Figure 8 Interleave Mode

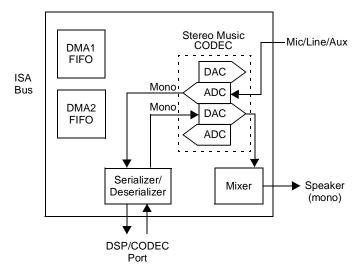

#### Other Modes

A typical Modem application is shown in Figure 9.

Figure 9 Modem Application

## **Concurrent Operation of Serial Interface**

For the ES689/ES690 interface, the ES1868 detects activity from the ES689/ES690 by the combination of MCLK being active and MSD-toggling within a period of 64 MCLKs. Unless bit 4 of Mixer Extension register 48h is zero, this activity means that the normal FM output is replaced by the signal coming in the serial port. All other ES1868 audio functions are unaffected.

For DSP serial mode (such as enabled by the SE pin), when it is not necessary to use the ES1868 DMA channel as part of the DSP application, then a concurrently running audio application such as a game or a Windows audio application can run without knowledge of the DSP application's acquisition of the analog section. Of course, since the DACs and ADCs are acquired by the DSP, they are not available for the audio application. In this case, sound output from the game or other application will be muted. For example, in a game playing audio data, the DMA from the game will continue to operate normally, but the data will be blocked from the DAC.

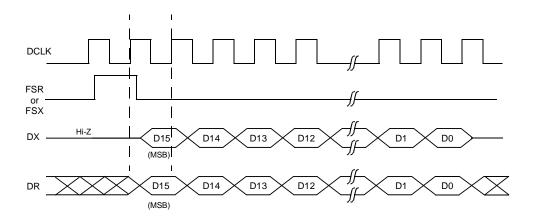

#### Serial Data Format

Figure 10 shows the format for serial data used with the DSP serial interface.

Figure 10 16-Bit Data, Positive Sync Pulse

#### **Modem Interface**

The ES1868 supports connection to an external modem.

#### Applicable Pins

The ES1868 has four pins dedicated to supporting an external modem. They are:

MMCSB Output from the ES1868 to an external modem chip select, active-low. The address space is determined by the PnP configuration. The Modem device uses eight consecutive addresses, with the base address, typically one of the COM ports.

MMIRQ Interrupt request from the Modem device. This signal is mapped to an IRQ output on the ES1868, based on the PnP configuration.

MMIEB Modem interrupt enable input. Active-low when the Modem interrupt is enabled. High when the Modem interrupt request is disabled. Generated from the Modem UART.

GPCS User-defined general-purpose chip select output, If selected by the PnP logic and based on the PnP configuration.

## **Modem Operating Modes**

If the modem DSP also requires a DMA channel, the GPI/GPO1 pins can be used for DRQ/-DACK from the modem.

The modem can also connect to the ES1868 through the DSP serial interface. This allows the modem to set the sample rate for both chips and have access to the microphone and speaker for speakerphone or voice-overdata applications. DSP determines the sample rate of the serial link by generating FSR/FSX pulses.

Figure 11 shows a typical modem interface application, a speakerphone or modem with voice-over-data.

Figure 11 Speakerphone or Modem w/Voice-Over-Data

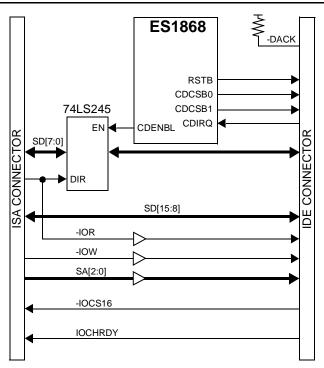

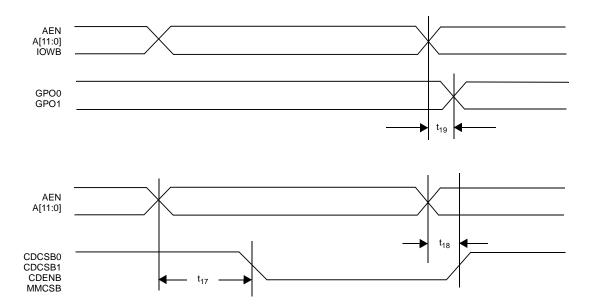

#### **IDE CD-ROM Interface**

#### Applicable Pins

There are four pins dedicated to supporting an IDE CD-ROM interface.

CDIRQ Interrupt request from CD-ROM. Internally routed to one of the six IRQ ISA outputs (A-F).

CDCSB0 Active-low decode output for eight command block registers. 24 mA driver.

CDCSB1 Active-low decode output for two control block registers. 24 mA driver.

CDENBL Active-low decode output for external 74LS245 transceiver that buffers the least 8 bits of the ISA data bus. This pin is active-low when CDCSB0, CDCSB1, or CD DMA -DACK is active-low.

In most cases, the IDE interface will not use DMA. If it *must* use DMA, then the GPO1/GPI pair (pins 91 and 92) can be used for this purpose. These pins would not be available for other external devices such as a modem/Audio Processor. Also, typically only one of the 4 DRQ/DACK pairs of the ES1868 would be connected to a 16-bit DMA channel. This does not give the PnP system any choice about assigning the CD DMA channel.

It is not recommended to use DMA for the CD-ROM.

Figure 12 IDE Interface – Typical Application

## **General-Purpose I/O Device**

In addition to modem and CD-ROM interfaces, the ES1868 Plug and Play logic supports one general-purpose I/O device. The GPO0 output can be configured to provide an active-high chip-select output when this device is accessed. The General-purpose device can decode 1, 2, 4, 8, or 16 consecutive addresses.

It is also possible to use GPI/GPO1 as a DMA channel for the General-purpose device if these pins are not used for the Modem or CD-ROM device.

In addition, the GPI pin can be used as an interrupt source for the general-purpose device if the pin is not otherwise used.

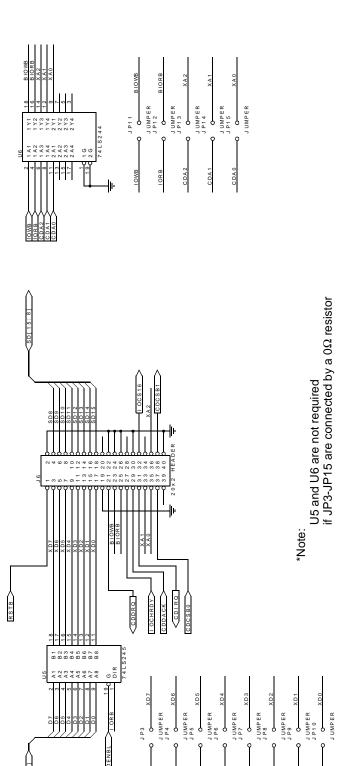

## Joystick/MPU-401 Interface

#### Applicable Registers

40H

#### MPU-401 UART Mode

There are two separate MIDI interfaces in the ES1868. The Sound Blaster compatible command set and a MPU-401 "UART Mode" compatible serial port. MPU-401 is a superior method of MIDI serial I/O because it does not interfere with DAC or ADC Sound Blaster commands. Both methods of serial I/O share the same MSI and MSO pins. The MPU-401 interface consists of separate 8-byte FIFOs for receive and transmit.

By default after hardware reset, the MPU-401 interface is disabled. It must be configured using Mixer Extension register 40h, which is described in the Joystick Device section.

MPU-401 requires an interrupt channel for MIDI receive. This interrupt should be selected using Mixer Extension register 40h. It should be different than the interrupt selected for audio DMA interrupts.

If MPU-401 is enabled, a low-level signal on pin MSI will prevent power-down and cause an automatic wake-up event if the ES1868 is powered down. Likewise, power-down is prevented if a byte is currently being received or transmitted.

Temporarily disabling MPU-401 using Mixer Extension register 40h acts as a reset to the FIFOs.

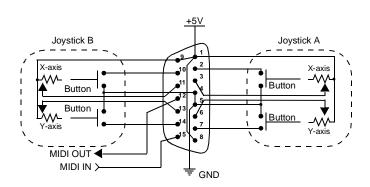

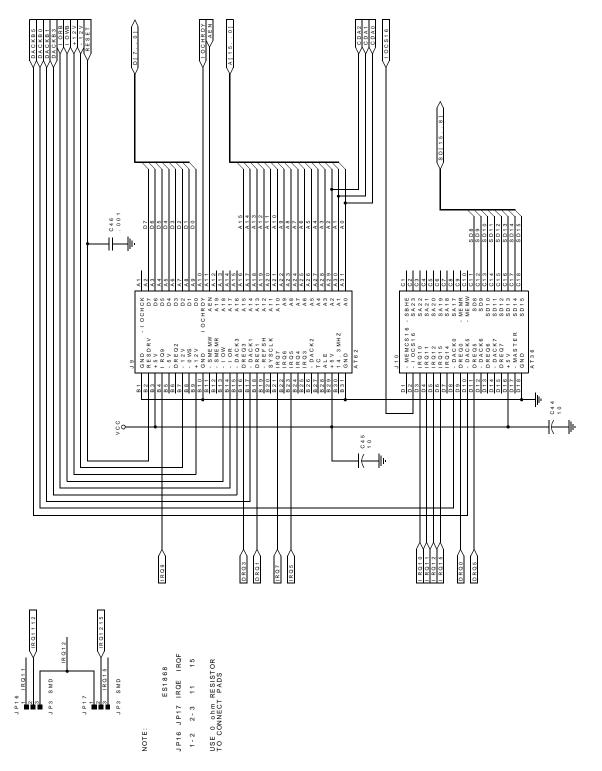

#### Joystick/MIDI External Interface

The joystick portion of the ES1868 reference design is identical to that on a standard PC game control adaptor or game port. The PC compatible joystick can be connected to a 15-pin D-sub connector. It supports all standard PC joystick-compatible software. If the system already has a game card or port, either remove the game card or disable the joystick port in the reference design by removing the joystick enable jumper. Disabling the joystick port does not affect its use as a MIDI port.

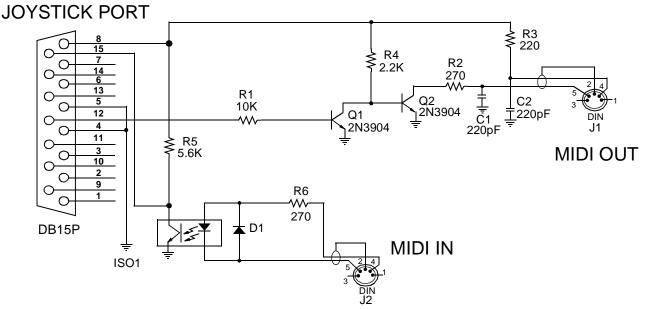

If support for multiple joysticks is required, a joystick conversion cable is needed. This cable uses a 15-pin D-sub male connector on one end, and two 15-pin D-sub female connector on the other end. All signals on this cable have direct pin-to-pin connection, except for pins 12 and 15. On the male connector, pins 12 and 15 should be left without connection. On the female connectors, pin 15 is internally connected to pin 8, and pin 12 is internally connected to pin 4. The dual joystick port and MIDI port take up only one slot in the system, leaving room for other cards. The dual joystick/MIDI connector configuration is shown below in Figure 13.

Figure 13 Dual Joystick/MIDI Connector

The MIDI Serial Interface Adaptor from the Joystick/MIDI Connector is shown in Figure 14.

Figure 14 MIDI Serial Interface

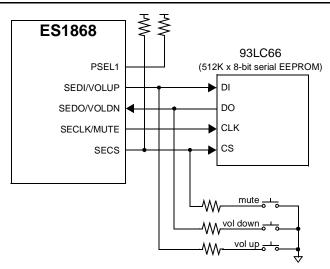

## **Serial EEPROM Interface**

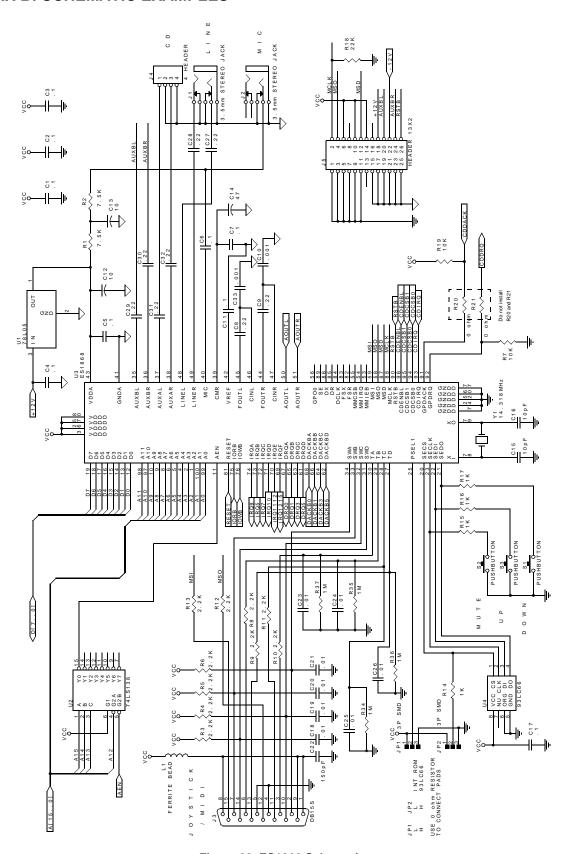

The ES1868 gets Plug and Play configuration data from an internal masked ROM or an external EEPROM device. The external EEPROM device is 512K x 8-bit in size.

The EEPROM interface is shared with the hardware volume controls. When the EEPROM interface is active, the volume controls are deactivated. See Figure 15.

The EEPROM can be read or written from the host processor. This allows the EEPROM to be reprogrammed or initially programmed during production test.

Pin 20, when used as SECS, is an input during reset. It is pulled low externally if an EEPROM exists and is to be used. Otherwise, it is pulled high, forcing use of the internal ROM.

After the reset command or hardware reset, 256 bytes from the EEPROM are read into the 256 x 8 FIFO RAM. SECLK becomes an output at 1 MHz. The address sent to the EEPROM will be either 00000000 or 10000000, based on the state of input PSEL.

Depending on the value of pins 25 and 20 and the operating mode selected for these pins, either the internal mask-ROM or the external EEPROM device is used.

| PSEL1 | SECS/<br>PSEL0 |              |         |                |

|-------|----------------|--------------|---------|----------------|

| 0     | 0              | Internal ROM |         |                |

| 1     | 1              | 93LC66       | 512 x 8 | 9 address bits |

#### **EEPROM ROM FORMAT**

| 'A5'        | Sync Byte            |  |  |  |  |  |

|-------------|----------------------|--|--|--|--|--|

| IRQB IRQA   | Mapping for $IRQB/A$ |  |  |  |  |  |

| IRQD IRQC   | Mapping for IRQD/C   |  |  |  |  |  |

| IRQF IRQE   | Mapping for $IRQF/E$ |  |  |  |  |  |

| DRQB DRQA   | Mapping for $DRQB/A$ |  |  |  |  |  |

| DRQD DRQC   | Mapping for $DRQD/C$ |  |  |  |  |  |

| PNP Reg 25h | Miscellaneous        |  |  |  |  |  |

| PNP Reg 26h | Miscellaneous        |  |  |  |  |  |

|             |                      |  |  |  |  |  |

Figure 15 Serial EEPROM - Typical Application

#### ANALOG DESIGN CONSIDERATIONS

This section describes design considerations related to inputs and outputs of analog signals and related pins on the chip.

#### **Game Port**

The game port address 201h is decoded for timer pins TA, TB, TC, and TD, and switch pins SWA, SWB, SWC, and SWD. The MIDI serial input and output also come from the game port connector in most applications.

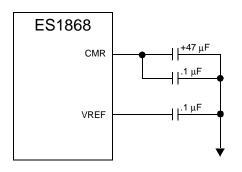

#### **Reference Generator**

Reference generator pins VREF and CMR are shown bypassed to analog ground.

Figure 16 Reference Generator Pin Diagram

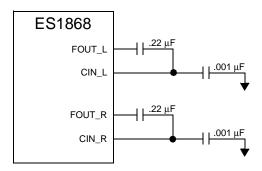

## **Switch-Capacitor Filter**

The outputs of the FOUT\_L and FOUT\_R filters must be AC-coupled to the inputs CIN\_L and CIN\_R, which provides for DC blocking and an opportunity for low pass filtering with capacitors to analog ground at these inputs.

Figure 17 Switch-Capacitor Filter Pin Diagram

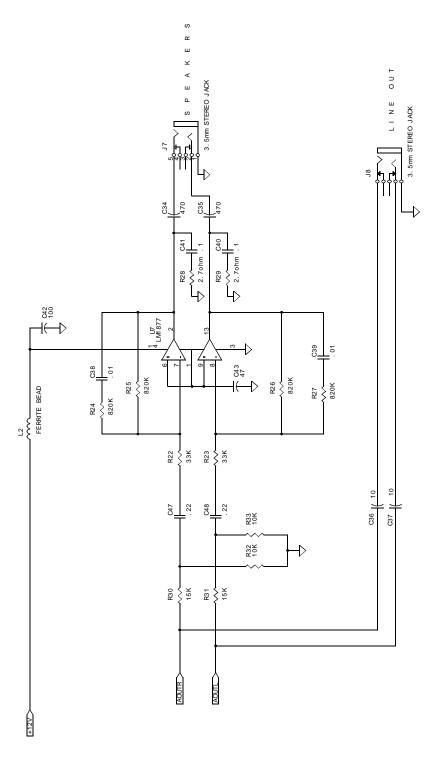

## **Audio Inputs and Outputs**

Analog inputs MIC, LINE\_L, LINE\_R, AUXA\_L, and AUXA\_R are to be capacitively coupled to their respective input signals. All have pull-up resistors to CMR.

ES1868 analog outputs AOUT\_L and AOUT\_R are intended to be AC-coupled to an amplifier, volume control potentiometer, or line-level outputs.

#### POWER MANAGEMENT OPERATING MODES

#### Overview

The ES1868 supports two normal operating modes and four power-management modes:

- · partial power-down mode

- full power-down mode

- · self-timed power-down

- · suspend/resume state

The decision to power down partially or fully is made by the system processor. To assist the system processor, activity flags are available that can be monitored by the system processor to track I/O activity to and from the ES1868. After a predetermined idle period, the ES1868 can be commanded to power-down partially or fully.

If the oscillator clock is provided from an external circuit, automatic wake-up upon I/O activity is available. With this feature, the act of reading or writing to an ES1868 I/O port will cause the chip to immediately power up without losing context from partial or fully powered-down states.

If the oscillator clock is provided by a crystal, automatic wake-up from partial power-down is still available because the oscillator will continue to run as long as the ES1868 is not fully powered down. Once the chip is fully powered down, however, automatic wake-up is not available with a crystal oscillator due to the start-up requirements of the oscillator itself. It is then the responsibility of the system software to provide for a start-up period for the oscillator before returning control to the application programs that may access the ES1868. In any case, there is no loss of context.

#### Using GPOs to Indicate Power-Down

The ES1868 has the ability to have one or both of the general-purpose outputs GPO0 and GPO1 change state when the ES1868 is powered-down.

After hardware reset, this feature is disabled and the general-purpose outputs are not affected by power-down. An indirect register in the ES1868 must be programmed to enable this feature.

Specifically, the GPO Power-down Control register is set by command 0CFh to port 227h and read by command 0CEh. It should be set once by system software after system reset. This register will remain unaffected by soft resets. Using this register, one or both of the general-purpose outputs can be programmed to be inverted from their normal state during power-down. The normal state of each pin is set by the appropriate bits in register 227h. A further feature allows the inverted outputs to return to their

normal state immediately after power up or after a programmed delay after power-up.

#### **GPO Power-Down Register**

| 7                          | 6                          | 5                          | 4                          | 3 | 2  | 1  | 0  |

|----------------------------|----------------------------|----------------------------|----------------------------|---|----|----|----|

| 1:restore<br>GPO1<br>timed | 1:invert<br>GPO1<br>at PDN | 1:restore<br>GPO0<br>timed | 1:invert<br>GPO0<br>at PDN | 0 | T2 | T1 | T0 |

| tiiriou                    | at i Dit                   | unioa                      | at i Div                   |   |    |    |    |

After hardware reset, all bits of this register are 0. This means that GPO0 and GPO1 are unaffected by the power-down status; that is, they remain in the state programmed into register 227h. If bit 6 (GPO1) or bit 4 (GPO0) is high, then the corresponding bit will be inverted from the normal state (register 227h) during power-down.

Bit 7 (GPO1) and bit 5 (GPO0), if low, indicate that the corresponding output will return to its normal state immediately after the ES1868 wakes up from power-down. If high, the corresponding output will return to its normal state after a time period elapses.

The time period is determined by bits 2:0 – T2, T1, T0: A 16 Hz counter will start at 0 and proceed up until it matches the 3-bit number formed by T2, T1, and T0. The maximum delay is 7 \* 67 milliseconds or about 469 milliseconds.

**Note:** "Power-down" as used in this document refers to full power-down, i.e., when both the analog and digital parts of the ES1868 are powered-down.

#### Partial Power-Down

In the partial power-down mode of operation, the power supply remains connected to the chip during power-down and the chip's analog section remains active while the digital circuits are mostly inactive.

The total current used by the ES1868 can be reduced by a factor of two or more by putting the ES1868 in a partial power-down state. The crystal oscillator, if used, will continue to operate. The analog circuitry remains powered up so that AUXA\_L, AUXA\_R, AUXB\_L, AUXB\_R, LINE\_L, LINE\_R, and MIC audio sources can continue to be heard. FM and DAC audio are automatically muted. There should be no pop when returning from partial power-down to a full power-up state.

The following items are active during partial power-down operation:

- 1. Oscillator is enabled.

- 2. MPU-401 operates.

- 3. PnP operates.

- 4. Configuration device operates.

- 5. H/W volume operates.

- 6. Mixer operates.

- 7. Analog operates.

- 8. Joystick operates.

- 9. Audio device is disabled, FM disabled.

- 10. Automatic wake-up with any I/O activity to FM or audio registers except 2x4h, 2x5h, 2x6h, 2x7h.

## **Causing Partial Power-Down**

To enter partial power-down mode, bit 3 of register 227h must be high before pulsing bit 2 high, then low, and bit 3 must remain high.

# Example: powering down the ES1868 using system software timer interrupt

In this example, it is assumed that the ES1868 is not using a crystal for its clock.

From a timer interrupt routine, read 226h to monitor activity. After one minute of I/O inactivity, it is decided that the ES1868 is to be powered down completely, then return from a timer interrupt. The ES1868 wakes up automatically upon any I/O access to the ES1868 by any application.

- 1. First, see if the ES1868 is already powered down (bit 3 of port 226h = 0). If so, there is nothing to do.

- Next, check if the ES1868 is being held in reset by reading bit 0 of port 226h. If bit 0 is high, the reset must be released before power-down can occur: Clear bit 0 of port 226h, then delay 1 millisecond or more for the ES1868 processor to complete its initialization.

- 3. Next, check to see if the ES1868 is in MIDI serial interface mode by testing bit 2 of port address 226h. If so, it may not be prudent to power-down. While the ES1868 can power-down when in MIDI mode, it will not automatically wake up if serial data comes in to the MSI pin, and such data will be lost.

- 4. Next, send a power-down request to the chip by clearing bit 3 in register 227h, then pulsing bit 2 first high, then low. The other bits of this register should be preserved. The ES1868 processor sees the rising edge of bit 2 of register 227h as an interrupt request to power-down.

## Waking from Partial Power-down

Any I/O activity will wake the ES1868 from a partial power-down. The following items are in effect upon waking from partial power-down:

- CSAUD + I/O except 2x6h read, 2x7h read/write.

- CSFM + I/O.

- Audio DACK + I/O.

- DSP or ES689/ES690 Serial Activity.

#### **Full Power-Down**

Complete power-down reduces the operating current to less than 50 microamps.

The following items are indicators of a full power-down operation:

- Nothing operates, except for some programmed I/O.

- The Activity Flags from a port 2x6h read are:

- Bit 7 Activity latch PnP, Joystick, MPU-401, Configuration, CD-ROM, Modem, or GPI/O or DMA activity.

- Bit 6 Activity latch: 2x4h, 2x5h I/O.

- Bit 5 Activity latch: Audio (except 2x4h, 2x5h, 2x6h read, 2x7h read/write), FM I/O or DMA.

- Bit 4 DSP and ES689/ES690 serial activity status.

#### Wake from Total Power-Down

There are three main ways to wake the chip up from full power-down:

- 1. hardware reset

- 2. software reset

- 3. I/O activity

#### Hardware Reset

The chip is automatically restored to activity upon a hardware reset. Context is not preserved.

#### Software Reset

Refer to the section "Resetting the ES1868 via Software" for information on the software reset sequence.

#### I/O Activity Causing Automatic Wake-up

Automatic wake-up is the method whereby the chip returns to the full power-up state, triggered by I/O activity. With automatic wake-up the context is preserved.

Any I/O access to any of the ES1868 port addresses other than 226h or 227h causes an automatic wake-up.

Automatic wake-up can also be triggered by DMA accesses. However, it is unlikely this will occur if power-down is triggered by a period of I/O inactivity, which includes DMA accesses and the I/O operations required to set up the DMA transfer.

Automatic wake-up requires that XI or EXTCLK is driven by a stable clock. This can either be an external clock source or from a crystal connected to XI and XO. In the latter case, the ES1868 cannot be fully powered down and have automatic wake-up work correctly. This is because the oscillator will require some time (typically greater than 25 milliseconds) to stabilize.

In the full power-down state the oscillator is stopped and the analog circuitry is powered down. The AOUT\_L and AOUT\_R pins are left at approximately the reference voltage by a high value resistor divider.

To wake the chip from a total power-down, set bit 4 of port 227h high for 25 milliseconds, then clear bit 3, ENXOSC, of port 227h. This enables the oscillator even when analog is powered down.

#### Inputs and Outputs During Power-Down

When powered-down, digital inputs that do not have pull-up or pull-down devices should be pulled high or low, that is, they should not be floating. An example would be placing pull-down resistors on pins such as A[11:0] and AEN.

Some input pins have circuitry that provides a pull-down device when the ES1868 digital circuits are powered up. During power-down, these inputs have a feedback device that latches the input state and prevents leakage current into the pin, effectively disabling the pull-down device. The pins that have this feature are SE and DR.

The CE pin has a similar feature using a pull-up device rather than a pull-down device.

Output pins such as DRQx and IRQx will be frozen in their state at power-down.

GPO0 and GPO1 may change state during full power-down if so programmed (see section below on programming GPO0 and GPO1 to reflect power-down status).

The MSI pin has an internal pull-up device, so this pin can be left floating during power-down.

The internal inverter connected to pins XI and XO will continue to operate when the digital portion of the ES1868 is powered-down as long as 1) SCLK is high, and 2) the analog portion is powered-up. When the chip is fully powered-down, the inverter becomes high-impedance with a weak pull-up on the XO pin.

The VREF output is driven low when the analog circuitry is powered-down.

CMR is pulled low by an internal transistor during analog power-down.

The AOUT\_L and AOUT\_R pins will be held at approximately the idle voltage level with a high-impedance resistor divider. After return to full power-up state from full power-down state, these pins are not enabled for 48-64 milliseonds. The chip should remain in full power-up state for at least 64 milliseconds to assure that the AOUT\_L and AOUT\_R pins are enabled before changing to the partial power-down state. Otherwise they may never get enabled.

For this reason it is not possible to go directly from full power-down to partial power-down and have AOUT\_L and AOUT\_R enabled.

#### **Self-Timed Power-Down**

The ES1868 processor can be programmed to monitor I/O activity in place of the system processor, and after a programmable period of inactivity, enter either a partial or full power-down state. Whether the ES1868 enters a partial or full power-down is determined by bit 3 of port 227h.

In this case, power is maintained as for partial or full power-down, except the decision to power-down is made by the ES1868 itself. In self-timed power-down, the ES1868 processor waits for a pre-programmed period of I/O inactivity between successive commands before entering partial or full power-down state. This mode is otherwise similar to partial or full power-down except that the decision to power-down is made by the ES1868 processor rather than the system processor. Even if self-timed power-down is enabled, the ES1868 can becommanded to power down by bit 2 of port 227h.

The ES1868 requires use of the activity flags in register 226h. Therefore, if this feature is enabled, the system processor will not be able to monitor I/O activity.

#### **Enabling Self-Timed Power-Down**

- 1. Send command C6h to enable access to this feature using the BDh command.

- 2. Send command BDh.

- Send the time out value N, where the time period is N x 8 seconds. If the value N is zero, self-timed powerdown is disabled.

- Send command C7h to disable access to this feature by the BDh command.

There is one limitation to this feature: the timing of inactivity only occurs between commands sent to the ES1868. It is possible for a program to leave the ES1868 in a state where timing will not happen. An example of this is if a program exits without completion of a DMA transfer. Most programs are well-behaved in this respect and leave the ES1868 with appropriate registers defined.

## Suspend/Resume

In the fourth power management category, power is removed from the ES1868 during its suspended state. Before removing power, the entire context of the processor and registers must be uploaded to the system processor and saved. After restoring power and generating a hardware reset, the opposite resume operation must download the context.

The term "suspend" is used here to describe the process of uploading the context of the ES1868 and removing digital

and analog power to the chip. The term "resume" describes the process of applying power to the ES1868 and downloading the context.

In firmware version 10 of the ES1868, 782 (decimal) bytes are required to store the entire context of the ES1868.

It is possible to suspend the ES1868 regardless of its current state, including suspending in the middle of a DMA transfer. The suspend process is initiated by pulsing bit 7 of port address 227h high, then low. This will interrupt the ES1868 processor and begin a sequence of upload operations.

A hardware reset is required during the resume procedure, before downloading the context. Downloading the context is initiated with command C1h.

A sample assembly language program that implements suspend and resume from a TSR is available from the applications department of ESS Technology.

## Pop Prevention in the External Amplifier

Normally, in order to directly drive speakers in an ES1868 design, an external stereo amplifier chip is used. There are two power management problems associated with an external amplifier:

- 1. The amplifier itself will draw current unless it can be powered down.

- 2. Suspend/resume will cause pops because power is removed from the ES1868 and then re-applied.

Amplifiers such as the SGS/Thomson TDA7233 have a mute input which reduces current to 400 microamps and also reduces pops from the suspend/resume process. This part is a mono amplifier, so two are required. Connect GPO0 to the active low MUTE input of the TDA7233. In this case the amplifier will be muted after hardware reset. In an program activated from the AUTOEXEC.BAT file, program the ES1868 so that GPO0 will be high when powered-up and low when fully powered-down. Program a delay of about 133 milliseconds between power-down and power-up states, before GPO0 returns high, to allow the ES1868 analog circuits to stabilize.

#### **Power Management and the FM Synthesizer**

The ES1868 FM synthesizer is a fully static design. This means that the clock can be stopped to power-down the circuitry without loss of the state.

Also, for suspend/resume applications, the entire context of the synthesizer can be read back. The details of this procedure are beyond the scope of this document and are covered in an application note concerning suspend/resume.

#### NORMAL OPERATING MODES

The ES1868 can be in one of two operating modes: (Sound Blaster) Compatibility Mode, and (ESS) Extended Mode.

In both modes, a set of mixer control registers allows application software to control the analog mixer, record source, and output volume. Programming the ES1868 Enhanced Mixer is described later in this document in the section on programming in Extended Mode.

## **Compatibility Mode Description**

As shown in Table 8, there are two ways to access the ADCs and DACs inside the ES1868. The first mode is called Compatibility Mode, where the ES1868 is compatible with both the ES488 and the Sound Blaster Pro. This is the default mode after any reset. In this mode the ES1868 processor is an intermediary in all functions between the ISA bus and the ADC and DAC. The blocks

labeled "FIFO/DMA Control" and "256-Byte FIFO" are inactive. The ES1868 processor performs limited FIFO functions using 64 bytes of internal memory.

## **Extended Mode Description**

The ES1868 also supports an Extended Mode of operation. In this case a 256-byte FIFO is used as an intermediary between the ISA bus and the ADC and DAC control registers, and various Extended Mode indirect registers are used for control. The ES1868 processor is mostly idle in this mode. DMA control is handled by dedicated logic. Programming for Extended Mode operation requires accessing various control registers with ES1868 commands. Some of these commands are also useful for Compatibility Mode, such as those that configure DMA and IRQ channels. Table 8 lists the features of the two modes.

**Table 8 Comparison of Operation Modes**

|                                               | Compatibility Mode<br>(Sound Blaster Pro) | Extended Mode                |

|-----------------------------------------------|-------------------------------------------|------------------------------|

| Sound Blaster Pro compatible                  | Yes                                       | No                           |

| FIFO Size                                     | 64 bytes (firmware managed)               | 256 bytes (hardware managed) |

| Mono 8-bit ADC, DAC                           | Yes, to 44 kHz                            | Yes, to 44 kHz               |

| Mono 16-bit ADC, DAC                          | Yes, to 22 kHz                            | Yes, to 44 kHz               |

| Stereo 8-bit DAC                              | Yes, to 22 kHz                            | Yes, to 44 kHz               |

| Stereo 8-bit ADC                              | Yes, to 22 kHz                            | Yes, to 44 kHz               |

| Stereo 16-bit DAC                             | Yes, to 11 kHz                            | Yes, to 44 kHz               |

| Stereo 16-bit ADC                             | No                                        | Yes, to 44 kHz               |

| Signed/Unsigned Control                       | No                                        | Yes                          |

| Automatic Gain Control during recording       | Firmware controlled, to 22 kHz, mono only | No                           |

| Programmed I/O block transfer for ADC and DAC | No                                        | Yes                          |

| FIFO status flags                             | No                                        | Yes                          |

| Auto reload DMA                               | Yes                                       | Yes                          |

| Time base for programmable timer              | 1 MHz or 1.5 MHz                          | 800 kHz or 400 kHz           |

| ADC and DAC jitter                            | ± 2 microseconds                          | None                         |

#### PROGRAMMING THE ES1868

## **Identifying the ES1868**

The ES1868 may be identified by reading Mixer Extension register 40h successively. It returns the following values on four successive reads:

18h, 68h, A[11:0], A[7:0]

where 18h and 68h are data reads indicating the part number (1868), and A[11:0] is the base address of the configuration device.

## Resetting the ES1868 via Software

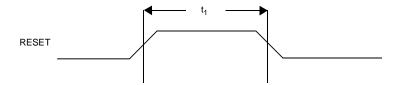

The chip can be reset in either of two ways: hardware reset and software reset. The hardware reset signal comes from the ISA bus. Software reset is controlled by bit 0 of port 2x6h.

To reset the ES1868 by software:

- 1. Write a 1 to port 2x6h.

- Delay a short period, for example, by reading back 2x6h.

- 3. Write a 0 to port 2x6h.

- 4. In a loop that lasts at least 1 milliseconds, poll port 2xEh bit 7 for read data availability.

- If bit 7 is high, read the byte from port 2xAh. Exit loop if the content is 0AAh; otherwise, continue polling.

Both hardware reset and software reset will:

- 1. Disable Extended Mode.

- 2. Reset the timer divider and filter registers for 8 kHz sampling.

- 3. Stop any DMA transaction in progress.

- 4. Clear any active interrupt request.

- Disable voice input of mixer (see the D1h/ D3h commands).

- Reset Compatibility Mode and Extended Mode DMA counters to 2048 bytes.

- Set analog direction to be DAC, with the DAC value set to mid-level.

- 8. Set input volume for 8-bit recording with Automatic Gain Control (AGC) to maximum.

- 9. Set input volume for 16-bit recording to mid-range

In addition to performing actions on the above list, a hardware reset will reset all Mixer registers to default values.

# **Configuring the ES1868**

## **PnP Configuration**

The ES1868 can be configured using the Configuration registers, which are Direct registers. These registers are listed in Table 9.

Table 9 Configuration Registers

| Address Offset | Name                           | Bits                                            | Function                                                                                                     | Values                                                                                                                                                  |

|----------------|--------------------------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Base+0h        | Configuration register address |                                                 |                                                                                                              |                                                                                                                                                         |

| Base+1h        | Configuration register data    |                                                 |                                                                                                              |                                                                                                                                                         |

| Base+2h        | EEPROM data register           |                                                 |                                                                                                              |                                                                                                                                                         |

| Base+3h        | EEPROM command register        | Bits 3:0                                        | Command                                                                                                      | 0 0 0 0 = Write disable<br>0 0 0 1 = Write all<br>0 0 1 0 = Erase all<br>0 0 1 1 = Write enable<br>0 1 0 0 = Write<br>1 0 0 0 = Read<br>1 1 0 0 = Erase |

| Base+4h        | Reset EEPROM address           |                                                 |                                                                                                              |                                                                                                                                                         |

| Base+5h        | Status register                | Bit 0<br>Bit 1<br>Bits 3:2                      | Reset sequence busy bit<br>PNPOK bit<br>State                                                                | 00 = wait_for_key<br>01 = sleep<br>10 = isolation<br>11 = configure<br>00 = internal ROM<br>11 = 512 x 8-bit                                            |

| Base+6h        | Interrupt Status register      | Bit 0 Bit 1 Bit 2 Bit 3 Bit 4 Bit 5 Bit 6 Bit 7 | Audio 1 Audio 2 Hardware volume MPU-401 CD-ROM interface Modem General-purpose reserved                      |                                                                                                                                                         |

| Base+7h        | Interrupt Mask register        | Bit 0 Bit 1 Bit 2 Bit 3 Bit 4 Bit 5 Bit 6 Bit 7 | Audio 1<br>Audio 2<br>Hardware volume<br>MPU-401<br>CD-ROM Interface<br>Modem<br>General-purpose<br>reserved |                                                                                                                                                         |

## **Compatibility Mode Programming**

This section describes Compatibility Mode programming considerations.

## **Compatibility Mode DAC Operation**

After reset, the analog circuitry is set up for DAC operations. Any ADC command will cause a switch to the ADC "direction," and any subsequent DAC command will switch the ES1868 back to the DAC "direction." The DAC output is filtered and connected to the voice input of the mixer. After reset, the voice input to the mixer is muted to prevent pops. The ES1868 maintains a status flag called the Voice-Enable/Disable flag that indicates when the voice channel is muted. Use command D1h to enable the voice channel and command D3h to disable the voice channel.

If you do not wish to reset the ES1868 before playing a new sound, and you are not certain of the status of the analog circuits, you can mute the voice input to the mixer with command D3h, then set up DAC direction and level using the direct-to-DAC command:

10h + 80h

Then wait 25 milliseconds for the analog circuitry to settle before enabling the voice channel with command D1H.

A pop sound may still be heard if the DAC level was left at a value other than mid-level (code 80h on an 8-bit scale) by the previous play operation. To prevent this, always finish a DAC transfer with a command to set the DAC level to mid-range:

10h + 80h

#### 8-Bit, 16-Bit, and Compressed Data Formats

The 8-bit samples are unsigned, ranging from 0 to 0FFh, with the DC level around 80h.

16-bit samples are unsigned, least byte first, ranging from 0000h to 0FFFFh with the DC level around 8000h.

The ES1868 supports two types of compressed sound DAC operations: ESPCM®, which uses a variety of proprietary compression techniques developed by ESS Technology, and ADPCM, which is supported by many other sound cards but is of a lower quality.

Both ADPCM and ESPCM® are only transferred using DMA transfer. The first block of a multiple-block transfer uses a different command than subsequent blocks. The first byte of the first block is called the reference byte.

#### **Direct Mode DAC vs. DMA Mode DAC**

In direct mode, the timing for DAC transfers is handled by the application program. For example, the system timer can be reprogrammed to generate interrupts at the desired sample rate. At each system timer interrupt, the command 10h (or 11h for 16-bit data) is issued followed by the sample. Polling of the Write-Buffer-Available flag is required before writing the command and between the command and the data.

**Note:** The switched capacitor filter is initialized by reset for an intended sample rate of 8 kHz. In direct mode, the application may wish to adjust this filter appropriate to the actual sample rate. The easiest way to do this is to program the timer with command 40h just as if the application were using DMA mode.

In DMA mode, the programmable timer in the ES1868 controls the rate at which samples are sent to the DAC. The timer is programmed using command 40h, which also sets up the programmable filters inside the ES1868. The ES1868 firmware maintains an internal FIFO (32 levels for 16-bit transfers, 64 levels for 8-bit transfers) that is filled by DMA transfers and emptied by the timed transfers to the DAC.

Before a DMA transfer, the application first programs the DMA controller for the desired transfer size and address, then programs the ES1868 with the same size information. At the end of the transfer, the ES1868 generates an interrupt request, indicating that the current block transfer is complete. The FIFO gives the application program sufficient time to respond to the interrupt and initiate the next block transfer.

In "normal mode" DMA transfers, the DMA controller must be initialized and the ES1868 be commanded for every block that is transferred. In "auto-initialize mode", the DMA transfer is continuous, in a circular buffer, and the ES1868 generates an interrupt for the transition between buffer halves. In this mode the DMA controller and ES1868 need to be set up only once.

The ES1868 supports mono 8-bit transfers to DAC at a rate up to 44 kHz. Mono 16-bit transfers are supported up to a rate of 22 kHz.

#### **Stereo DAC Transfers in Compatibility Mode**

Stereo DAC transfers are only available using DMA rather than direct mode commands.

To perform a stereo DAC transfer, first set bit 1 of Mixer register 0Eh high. Then set the timer divider to twice the per-channel sample rate. The maximum stereo transfer rate for 8-bit data is 22 kHz per channel, so for this case program the timer divider as if it were for 44 kHz mono. The maximum stereo transfer rate for 16-bit data is 11 kHz per channel.

For 8-bit data, the ES1868 expects the first byte transferred to be for the right channel, and subsequent bytes to alternate left, right etc.

For 16-bit data, the ES1868 expects the DMA transfers to be a multiple of 4, with repeating groups in the order:

- 1. left low byte

- 2. left high byte

- 3. right low byte

- 4. right high byte

Clear bit 1 of Mixer register 0Eh when the DAC transfer is complete.

#### **Compatibility Mode ADC Operation**

The ES1868 analog circuitry is switched from the DAC direction to the ADC direction by the first direct or DMA mode ADC command. Discard the first 25 to 100 milliseconds of samples if possible because pops might occur in the data due to the change from the DAC to ADC direction. In the ADC direction the voice input to the mixer is automatically muted.

The ES1868 has four recording sources: Microphone, Line, Aux/CD, and Mixer. Microphone input is the source after any reset. Select the source using the mixer control register 0Ch/1Ch.

The selected source passes through an input volume stage that can be programmed with 16 levels of gain from 0 to +22.5 dB in steps of 1.5 dB. In 8-bit recordings (other than "high speed mode") the volume stage is controlled by the ES1868 firmware for the purposes of AGC. In 16-bit recordings as well as "high speed mode" 8-bit recordings, the input volume stage is controllable from application software. Use command DDh to set the input volume level from 0 to 15. The reset default is mid-range, 8.

The ES1868 supports direct mode ADC, "normal mode" DMA for ADC, as well all "auto-initialize mode" DMA for ADC. The differences between the various types are described above for DAC.

**Note:** The switched capacitor filter is initialized by reset for an intended sample rate of 8 kHz. In direct mode, the application may wish to adjust this filter appropriate to the actual sample rate. The best way to do this is to program the timer with command 40h just as if the application was

using DMA mode.

The maximum sample rate for direct mode ADC is 22 kHz.

The maximum sample rate for DMA ADC for both 8-bit and 16-bit is 22 kHz, using commands 24h, 25h, 2Ch or 2Dh.

There is a special "high speed mode" for ADC that allows 8-bit sampling up to 44 kHz. This mode uses commands 98h (auto-initialize) and 99h (normal). No AGC is performed: the input volume is controlled with command DDh.

# **Sending Commands During Compatibility Mode DMA Operations**

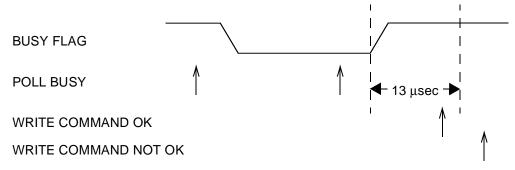

The ES1868 has an internal 64-byte FIFO used for DMA to the DAC and from the ADC. When the FIFO is full (in the case of DAC, empty in the case of ADC), DMA requests are temporarily suspended and the Busy flag (bit 7 of port 2xCh) is cleared. This allows a window of opportunity to send a command to the ES1868. Commands such as D1h and D3h control the mixer Voice-Enable/Disable status, and command D0h suspends or pauses DMA.

The ES1868 chip sets the Busy flag when the command window is no longer open. Application software must send a command within 13 microseconds after the Busy flag goes high or the command will be confused with DMA data. This is normally easy to do if the polling is done with interrupts disabled.

As an example of sending a command during DMA, consider the case where the application desires to send command D0h in the middle of a DMA transfer. The application disables interrupts and polls the Busy flag. Because of the FIFO and the rules used for determining the command window, it is possible for the current DMA transfer to complete while waiting for the Busy flag to clear. In this event, the D0h command has no function, and a pending interrupt request from the DMA completion is generated. The interrupt request can be cleared by reading port 2xEh before enabling interrupts.

Figure 18 shows timing considerations for sending a command.

Figure 18 Command Transfer Timing

# **Extended Mode Programming**

This section describes Extended Mode programming considerations.

Extended Mode registers are indirect registers, that is, they are written to and read from using commands sent to a port.

# **Mixing Modes Not Recommended**

Avoid mixing Extended Mode commands with Compatibility Mode commands where possible. The Voice-Enable/Disable commands D1h and D3h are safe to use when using Extended Mode to process ADC or DAC. However, there are other Compatibility Mode commands that are likely to cause problems. The Extended Mode commands may be used to set up just the DMA or IRQ channels before entering the Compatibility Mode.

# Commanding the ES1868 Extended Registers

This section describes how to send commands and command-related data to the ES1868's extended registers, which are indirect registers.

# **Enabling Extended Mode Commands**

After any reset, and before using any Extended Mode commands you must first send command C6h to enable Extended Mode operation.

Commands of the format Axh or Bxh, where x is a numeric value, are used for Extended Mode programming, and are used to access the 'internal' or *indirect* registers of the ES1868. For convenience, the registers are named after the commands used to access them. For example, "register A4h", the DMA counter low byte register, is written to via "command A4h".

#### Writing ES1868 Internal Registers

The following show an example of writing to an ES1868 internal: to set up the FIFO DMA Counter Reload register to F800h, send the following command/data bytes:

A4h, 00h; register A4h = 0h A5h, F8h; register A5h=F8h

Always check the write buffer before writing a command to port 2xCh, to make sure it is not busy. Also, be sure to send command C6h after every reset when using Extended Mode commands.

#### Reading ES1868 Internal Registers

Command C0h is used to read the ES1868 internal registers in Extended Mode. Send command C0h followed by the register number, Axh or Bxh. For example, to read register A4h, send the following command bytes:

C0h, A4h

Then poll the Read-Data-Buffer-Status bit, bit 7 of port 2xEh, before reading the register contents.

# **Command/Data Handshaking Protocol**

#### Writing Commands to the ES1868

Commands written to the ES1868 enter a write buffer. Before writing the command, make sure the buffer is not busy.

Bit 7 of port 2xCH is the ES1868 Busy flag. It is set when the write buffer is full or when the ES1868 is otherwise busy (for example, during initialization after reset or during Compatibility Mode DMA requests).

To write a command or data byte to the ES1868 processor:

- 1. poll bit 7 of port 2xCh until it is clear

- 2. write the command/data byte to port 2xCh.

**Note:** The port 2xCh Write Buffer is shared with Compatibility Mode DMA write operations. When DMA is active, the Busy flag is cleared during time windows when a command can be received. Normally, the only commands that should be sent during DMA operations are 0Dxh commands such as DMA-Pause/Continue, Voice-Enable/Disable, etc. In this situation it is recommended that interrupts be disabled between the time that the Busy bit is polled and the command is written. Also, the time between these instructions should be minimized. For more information, see the section titled "Sending Commands During Compatibility Mode DMA Operations".

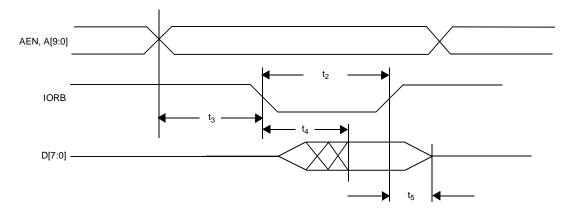

#### Reading the Read Data Buffer of the ES1868

The Read-Data-Buffer-Status flag can be polled by reading bit 7 of port 2xEh. When a byte is available the bit is set high. Note that any read of port 2xEh will also clear any active interrupt request from the ES1868. An alternative way of polling the read buffer status bit is via bit 6 of port 2xCh, which is the same flag. The buffer status flag is cleared automatically by reading the byte from port 2xAh.

# **Summary of Commands for Extended Mode**

When the ES1868 is in Extended Mode, it accepts commands for the extended (indirect) registers.

Table 10 lists the commands accepted by the ES1868 in this mode.

Table 10 Command Summary

| Command | Data Byte(s)<br>Write/Read | Function                                                                                                                                                                                                                         |  |  |  |  |

|---------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 10h     | 1 write                    | Direct write 8-bit DAC. Data is 8-bit unsigned format.                                                                                                                                                                           |  |  |  |  |

| 11h     | 2 writes                   | Direct write 16-bit DAC. Data is 16-bit unsigned format, first low byte then high byte.                                                                                                                                          |  |  |  |  |

| 14h     | 2 writes                   | Start normal mode DMA for 8-bit DAC transfer. Data is transfer count - 1, least byte first. Stereo DAC ransfer if stereo flag is set in Mixer register 0Eh. Maximum sample rate is 44 kHz mono, 22 kHz stereo.                   |  |  |  |  |

| 15h     | 2 writes                   | Start normal mode DMA for 16-bit DAC transfer. Data is transfer count - 1, least byte first. Stereo DAC transfer if stereo flag is set in Mixer register 0EH. Maximum sample rate is 22 kHz mono, 11 kHz stereo.                 |  |  |  |  |

| 1Ch     |                            | Start auto-initialize mode DMA for 8-bit DAC transfer. Block size must be previously set by command 48h. Stereo DAC transfer if stereo flag is set in Mixer register 0Eh. Maximum sample rate is 44 kHz mono, 22 kHz stereo.     |  |  |  |  |

| 1Dh     |                            | Start auto-initialize mode DMA for 16-bit DAC transfer. Block size must be previously set by command 48h. Stereo DAC transfer if stereo flag is set in Mixer register 0Eh. Maximum sample rate is 22 kHz mono, 11 kHz stereo.    |  |  |  |  |

| 20h     | 1 read                     | Direct mode 8-bit ADC. Data is 8-bit unsigned. Firmware controlled input volume for AGC.                                                                                                                                         |  |  |  |  |

| 21h     | 2 read                     | Direct mode 16-bit ADC, returns least byte first. Data is 16-bit unsigned format. Input volume controlled by command DDh.                                                                                                        |  |  |  |  |

| 24h     | 2 writes                   | Start normal mode DMA for 8-bit ADC transfer. Data is transfer count - 1, least byte first. Firmward controlled input volume for AGC. Maximum sample rate is 22 kHz: use command 99h for higher rates up to 44 kHz.              |  |  |  |  |

| 25h     | 2 writes                   | Start normal mode DMA for 16-bit ADC transfer. Data is transfer count - 1, least byte first. Input volume controlled via command DDh. Maximum sample rate is 22 kHz.                                                             |  |  |  |  |

| 2Ch     |                            | Start auto-initialize mode DMA for 8 bit ADC transfer. Block size must be previously set by command 48h. Firmware controlled input volume for AGC. Maximum sample rate is 22 kHz: use command 98h for higher rates up to 44 kHz. |  |  |  |  |

| 2Dh     |                            | Start auto-initialize mode DMA for 16-bit ADC transfer. Block size must be previously set by command 48h. Input volume is controlled by command DDh. Maximum sample rate is 22 kHz.                                              |  |  |  |  |

| 30h/31h |                            | MIDI input mode. Detects MIDI serial input data and transfers to data register, setting Data-Available flag in register 2xEh. Command 31h will also generate an interrupt request for each byte received.                        |  |  |  |  |

|         |                            | Exit MIDI input mode by executing a write to port 2xCh. The data written is ignored. A software reset will also exit this mode.                                                                                                  |  |  |  |  |

| 34h/35h |                            | MIDI UART mode. Acts like commands 30h/31h, except that any data written to 2xCh will be transmitted as MIDI serial output data. The only way to exit this mode is through software reset.                                       |  |  |  |  |

| 38h     | 1 write                    | MIDI output. Transmit one byte.                                                                                                                                                                                                  |  |  |  |  |

| 40h     | 1 write                    | Set time constant, X, for timer used for DMA mode DAC/ADC transfers: rate = 1 MHz / (256-X) X must be less than or equal to 233. For stereo DAC, program sample rate for twice the per-channel rate.                             |  |  |  |  |

| 41h     | 1 write                    | Alternate set time constant, X: rate = 1.5 MHz / (256-X)                                                                                                                                                                         |  |  |  |  |

|         |                            | This command provides more accurate timing for certain rates such as 22,050. X must be less that equal to 222. For stereo DAC, program sample rate for twice the per-channel rate.                                               |  |  |  |  |

| 42h     | 1 write                    | Set filter clock independently of timer rate. (note that the filter clock is automatically set by commands 40h/41h) Filter clock rate: rate = 7.16E6 / (256-X)                                                                   |  |  |  |  |

| _       |                            | The relationship between the low-pass filter -3 dB point and the filter clock rate is approximately 1:82.                                                                                                                        |  |  |  |  |

| 48h     | 2 writes                   | Set block size-1 for high speed mode and auto-init mode transfer, least byte first.                                                                                                                                              |  |  |  |  |

Table 10 Command Summary (Continued)

| Command          | Data Byte(s)<br>Write/Read | Function                                                                                                                                                                                                                                              |  |  |  |

|------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 64h              | 2 writes                   | Start $ESPCM^{\otimes}$ 4.3-bit (low compression) format DMA transfer to DAC. Data is transfer count - 1, least byte first.                                                                                                                           |  |  |  |

| 65h              | 2 writes                   | Same as command 64h, except with reference byte flag.                                                                                                                                                                                                 |  |  |  |

| 66h              | 2 writes                   | Start ESPCM® 3.4-bit (medium compression) format DMA transfer to DAC. Data is transfer count - east byte first.                                                                                                                                       |  |  |  |

| 67h              | 2 writes                   | Same as command 66h, except with reference byte flag.                                                                                                                                                                                                 |  |  |  |

| 6Ah              | 2 writes                   | Start ESPCM® 2.5-bit (high compression) format DMA transfer to DAC. Data is transfer count - 1, least byte first.                                                                                                                                     |  |  |  |

| 6Bh              | 2 writes                   | Same as command 6Ah, except with reference byte flag.                                                                                                                                                                                                 |  |  |  |

| 6Eh              | 2 writes                   | Start ESPCM® 4.3-bit (low compression) format ADC, compression, and DMA transfer. Data is transfer count - 1, least byte first.                                                                                                                       |  |  |  |

| 6Fh              | 2 writes                   | Same as command 6Eh, except with reference byte flag.                                                                                                                                                                                                 |  |  |  |

| 74h              | 2 writes                   | Start ADPCM 4-bit format DMA transfer to DAC. Data is transfer count - 1, least byte first.                                                                                                                                                           |  |  |  |